Ibrahim Qashqoush - Design Engineer

I am Ibrahim Qashqoush, a PhD student at Haifa University and a Lead Design Engineer at Cadence. My research focuses on compilers, high-level synthesis, computer architectures, and parallel computing.

Experience

Lead Design Engineer

Cadence Design

2024 - Present

Computer science Teacher

2017 - 2021

Design Engineer

Cadence Design

2022 - 2024

Senior engineering ,R&D engineering , CTO group

Western Digital

2021 - 2022

publications & conference

A short summary of my recent conferences and publications.

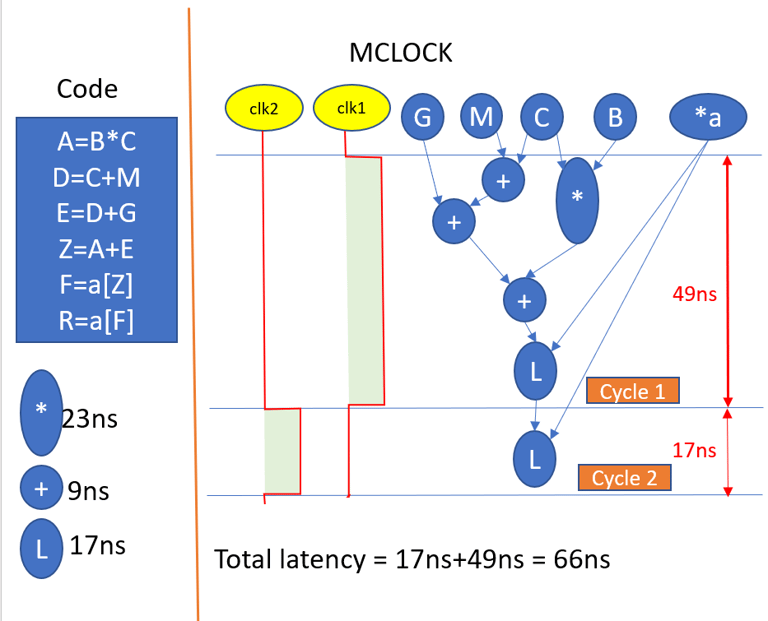

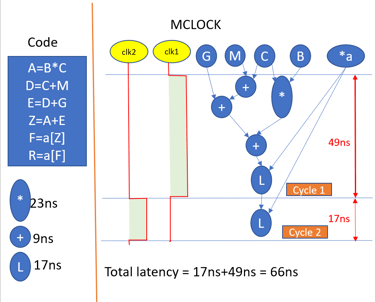

Using Multiple Clocks in High-Level Synthesis to Overcome Unbalanced Clock Cycles

Presented at IEEE MCSoC 2023

A novel LLVM-based HLS scheduling method that uses overlapping multi-clock execution to eliminate unbalanced cycle waste—achieving up to 16× faster hardware execution than commercial tools

Explore my peer-reviewed papers, conference talks, and slides.

🔗 View Publications Page →

Contact Me

Feel free to reach out for collaboration, inquiries, or to discuss my research and projects.

About

Ibrahim Qashqoush's personal portfolio and CV.

Connect

Explore

+972512358314

© 2025. All rights reserved.